E Deus disse “façam-se os bits” e assim surgiu a Eletrônica Digital!

Parte VII – As famílias lógicas – conclusão

Não é conta de mentiroso, mas chegamos a parte VII do nosso mini curso de Introdução a Eletrônica Digital.

No post anterior tratei da família TTL e de tudo que foi explicado nele, de forma bem superficial (tem muito mais coisa), mas o que é realmente importante é saber qual a tensão de polarização que se deve utilizar e conhecer os valores das tensões que serão interpretados como níveis lógicos. Estas informações serão de extrema valia na hora da reparação.

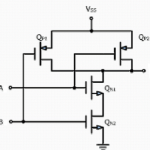

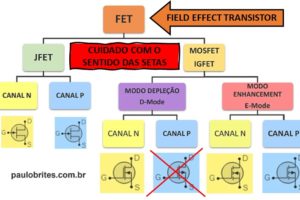

A outra família lógica importante é conhecida como CMOS que corresponde à sigla de Complementary Metal-Oxide Semicondoctor e como se pode perceber seus integrados são construídos não com os transistores bipolares como nos TTLs, e sim com transistores MOSFETs utilizando pares complementares (canal N e canal P).

No circuito podemos ver como é a estrutura interna de uma porta AND utilizando a tecnologia CMOS.

Mas, não se assuste porque, diferentemente da eletrônica analógica, não precisaremos entender o que cada transistor faz no circuito. Basta saber qual o papel de cada pino no CI e as tensões envolvidas, da mesma forma como fizemos com os TTLs.

O CMOS na Informática

O pessoal de informática deve estar associando a sigla CMOS com algo que eles estão acostumados a ver nas placas de computador.

Realmente esta associação procede. O que ficou conhecido na informática como “CMOS” na verdade é uma pequena memória RAM construída com a tecnologia MOS. Esta memória grava alguns dados de configuração da BIOS e data e a hora que são atualizados pelo RTC (Real Time Clock).

Por se tratar de uma memória RAM (que será estudada em um próximo post) ela é volátil e por isso, necessita de uma bateria para alimentá-la quando o computador é desligado.

Por que inventaram os CMOS?

O principal problema dos TTLs primitivos era o excessivo consumo de corrente o que exigia fontes de alimentação bem “parrudas” para alimentar placas com dezenas ou até centenas de CIs.

O avanço da tecnologia MOS trouxe componentes capazes de operar com correntes bem mais baixas e com impedâncias de entrada mais altas o que fez com que eles assumissem uma posição cada vez mais destacada no mundo dos dispositivos eletrônicos.

Outra vantagem trazida pelos CMOS foi a flexibilidade na tensão de alimentação.

Enquanto os TTLs exigem os “rígidos” 5V para sua alimentação, bem como pouca margem nos valores de tensão considerados como níveis lógicos 1 e 0, os CMOS são mais flexíveis.

Os CMOS podem trabalhar com tensão de polarização entre 3 a 15V (em alguns casos até 18V) o que sem dúvida dá mais flexibilidade ao projetista.

Entretanto, o reparador precisa estar atento para o fato de que os CIs da família CMOS, embora tenham uma codificação padronizada por CD40XX diferentemente dos TTL, às vezes, podem apresentar variações de parâmetros de um fabricante para outro. Sendo assim, ao se substituir um CMOS numa reparação talvez necessário fazê-lo por outro que além de ter o mesmo código seja do mesmo fabricante.

Entretanto, o reparador precisa estar atento para o fato de que os CIs da família CMOS, embora tenham uma codificação padronizada por CD40XX diferentemente dos TTL, às vezes, podem apresentar variações de parâmetros de um fabricante para outro. Sendo assim, ao se substituir um CMOS numa reparação talvez necessário fazê-lo por outro que além de ter o mesmo código seja do mesmo fabricante.

Os níveis lógicos dos CMOS

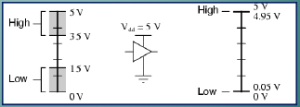

Da mesma forma como fizemos com os TTLs vamos apresentar os valores de tensão que serão considerados como níveis lógicos 1 e 0.

No caso dos CMOS Estes valores estarão atrelados ao valor da tensão de alimentação do CI uma vez que, diferentemente dos TTLs que têm um valor fixo de 5V, esta tensão pode variar entre 3 e 15V (ou 18V em alguns casos) como já foi dito.

Como a tensão de alimentação de um CMOS pode variar entre 3 e 15V vamos identifica-la por VDD.

Para os CIs da família CMOS a tensão correspondente ao nível lógico 1 (high) poderá variar entre 2/3(dois terços) do VDD até, no máximo, o valor de VDD. Quanto ao nível lógico 0 (low) ele fica entre 0V e até 1/3 (um terço) do VDD.

Vamos destrinchar isto com um exemplo.

Suponhamos que a tensão escolhida para um circuito que trabalhe com CMOS seja 12V.

Então qualquer tensão entre 8V (2/3 de 12) e 12V será interpretada como nível lógico alto (high), ou seja, bit 1.

Valores de tensão entre 0 e 4V (1/3 de 12) serão interpretados como nível baixo (low), ou seja, bit 0.

Na prática estes valores assumem uma pequena variação de 0,05V.

No caso do exemplo, o valor máximo de tensão do nível alto seria 11,95V e o valor mínimo do valor de tensão do nível baixo ficará em 0,05V.

A figura abaixo ilustra os níveis lógicos de um CMOS alimentado com VDD = 5V caso o circuito utilizasse as duas tecnologias, isto é, CMOS e TTL simultaneamente.

Na prática

Espero que você esteja percebendo que trabalhar com Eletrônica Digital é bem mais fácil do que com a Analógica.

Você não precisa reclamar que o esquema não tem os valores de tensão uma vez que estes valores são bem definidos e conhecidos uma vez que saibamos com que família lógica estamos lidando.

Para simplificar as medidas o melhor é trabalhar com uma ponta lógica no lugar do voltímetro.

Há alguns anos atrás a Minipa oferecia uma ponta lógica bem prática de se usar, mas infelizmente parece que eles retiraram este produto do mercado.

Brevemente vou apresentar aqui no site um circuito simples e a orientação para construir uma ponta lógica do tipo “eu que fiz” que, certamente lhe será muito útil. Aguarde não vai demorar muito.

Antes de encerar quero anunciar um brinde para você.

Basta colocar seu nome e e-mail no box que aparece à direita da tela e receberá grátis uma cópia do meu livro “Era Uma Vez um Resistor Queimado” (não é um conto de fadas rsrsrsrs).

Até sempre.

8 Comentários